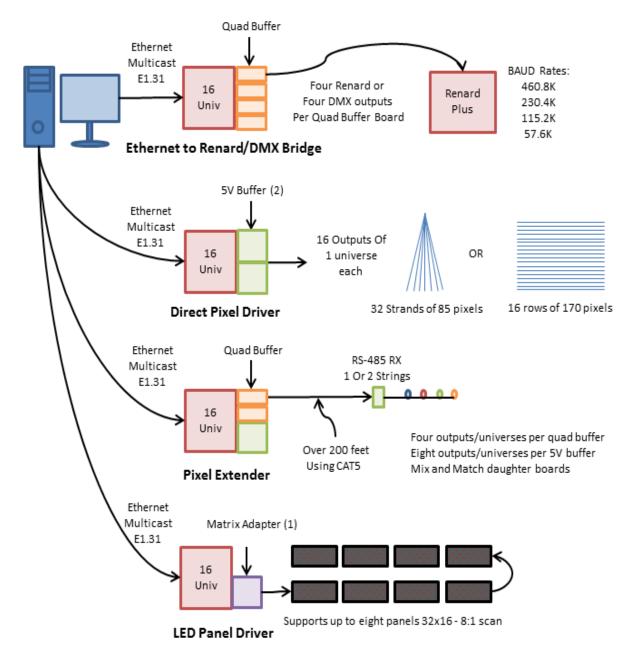

**Application Block Diagrams**

Welcome to one of the most versatile pixel controller available. This controller supports the conversion of multi-cast E1.31 Ethernet to many pixel formats, Renard and DMX. Now you do not have to buy separate controller for AC control and pixels. The board also supports LED matrix panels, so it can be configured for many applications. The outputs on the board allow you to customize the outputs to meet your needs.

SPECIFICATIONS: Supports multi-cast Ethernet E1.31 Supports 16 universes of 512 channels each, 170 pixels (RGB) Support 8 matrix LED panels 16x32 (8 to 1 scan) 16M colors, 85 Hertz refresh High performance controller, no dropped packets, scan rates up to 5mS Supports gamma correction (matches colors on computer) Supports both 5V and 12V strings

Renard serial at 56.7K, 115.2K, 230.4K, 460.8K DMX (Supports WS2822) WS2801 and compatible WS2811 and compatible WS2812B TM1804 (untested) TM1803/TM1809 (untested) TM1829 (untested)

An FPGA is a poor man's custom digital chip. These chips are much better suited to controlling pixel's, since they can easily manage many processes at the same time. The board is a simple two layer printed wiring board to connect the daughter cards to a standard 14-pin connector for output of the universes. The board has eight 14-pin connectors with 4 universes each. These output connectors allow universes to be added as required for your lighting application. Normally, the output connector will go to a buffer board which can support any type of output buffer and power as required for your application.

The best part of having an FPGA for the output of the pixels strings is that there are actually 16 output controllers that operate in parallel. So once the first byte of a message has arrived, the output machine is send the data to your pixels. The controller supports any number of channels for each output. So for the WS2801, that have a cycle time of 1.2 uS, the data is sent out in 1.2uS \* 8 \* 512 which equals about 5mS, which is a cycle time of 200 hertz. So you can update your pixels at a very fast rate.

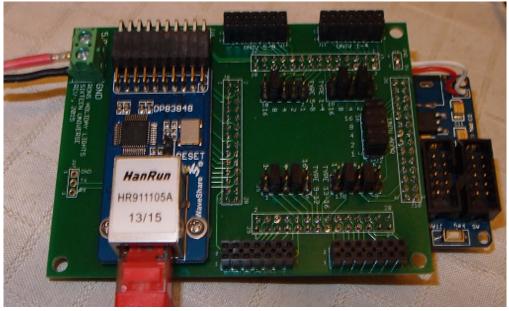

Sixteen Universe Controller Board, Rev A

The off the shelf FPGA module and Ethernet module allow this kit to be user friendly for the do it yourself user. The difficult to solder components are already soldered to the two daughter boards. So all you need to do is solder headers.

# SWITCHES & LEDS:

The reset switch is the small pushbutton on the FPGA card. The switches and LED have the following functions:

| RESET | - Universe test (all channels 1/4 brightness) |

|-------|-----------------------------------------------|

|       |                                               |

- LED1 Lights when Ethernet traffic is available for controller.

- LED2 Clock from Ethernet module good (Blinking at 5 hertz).

- LED3 Alternate clock blinking (Blinking at 5 hertz).

## ETHERNET MODULE:

Ethernet Board

The Ethernet module interfaces to the FPGA with RMII physical interface. The FPGA is designed to function only at 100Mbit/sec. Both the green and yellow LED should illuminate when the module is connected to the computer. If the yellow light does not lite, it indicates that the link is 10Mbit/sec. The green light will flash during Ethernet traffic. Note, that this controller does not support the IGMP messages.

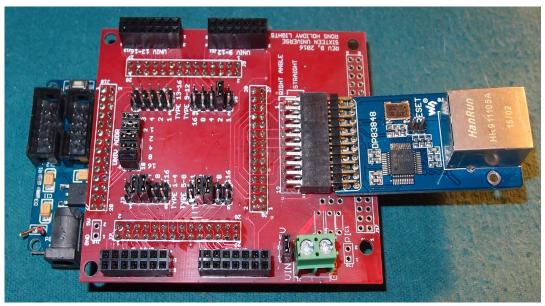

With both revision A and B it is important to insure that there is enough spacing between the Ethernet board and the top of the motherboard. Revision B supports two methods of mounting, using a right angle header as shown below.

Revision B, with Right Angle Header

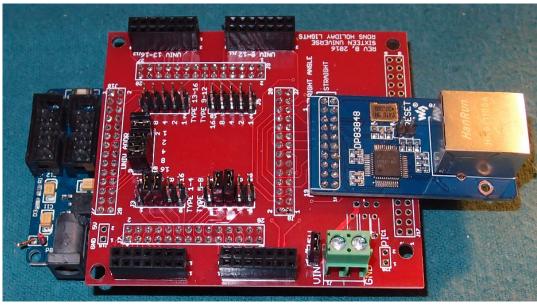

My preference for revision B is to remove the right angle connector and install a straight connector. In either case the board is marked with the correct location to install the Ethernet board. This installation type is more rigid and does not require standoffs as shown in the picture below.

Revision B, Using Straight Header

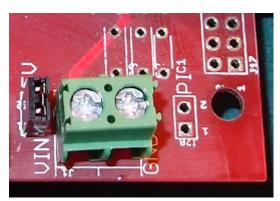

# **INPUT POWER:**

The input power for revision A is +5.0Vdc through the terminal block. The input is routed through a diode to protect the FPGA daughter card from reverse input voltages. The power draw will be approximately 0.08 ampere for the FPGA and the Ethernet board, plus power for the buffer cards. The +5.0Vdc is routed directly to the universe headers. So there is no protection for the daughter cards.

Revision B can also be run off a 5Vdc input as shown in the figure below. The 5V header must either have a jumper installed or a wire.

5Vdc Power Header

Revision B also supports higher input power, where the voltage regulator and three capacitors (C1, C2, C3) are installed on the board along with the voltage regulator. The voltage regulator is rated from 7V to 36Vdc power input. With the voltage regulator installed, do not install the 5Vdc header, as shown in the picture.

12Vdc Power

As shown in the 12Vdc power header picture, the jumper J20 will connect the Raspberry PI power to the controller board. This allows you to power the PI separately or through the controller.

Headers

The configuration of the outputs is accomplished through jumpers.

| Output type configuration.            |

|---------------------------------------|

| Standard output headers (3.3Vdc CMOS) |

#### Base multi-cast universe for reception of data.

#### Universal Output Header

The output connector for each universe is shown above. The pins are selected to allow the connector to be inserted backwards and still have the same power and ground connections. However, the universe outputs will not be correct. Two output pins are available for each of the universes.

#### PINS Description

- 1,14 5.0Vdc

- 4,5 Ground

- 10,11 Ground

- 2 Universe 1A (Data output)

- 3 Universe 1B (Clock output, if required)

- 6 Universe 2A

- 7 Universe 2B

- 8 Universe 3A

- 9 Universe 3B

- 12 Universe 4A

- 13 Universe 4B

#### **GAMMA CORRECTION:**

Gamma correction is selected by not installing jumper 16 for HEADER A. When the jumper is installed there is no gamma correction. This is a pullup resistor input to the FPGA, which may be changed with power on. Gamma correction was removed after version A, since this feature is available in most software.

# LED's:

LED's D2 and D4 will alternate flash on the FPGA board when it is correctly programmed. LED D5 will flash when data is within the multi-cast range of the board.

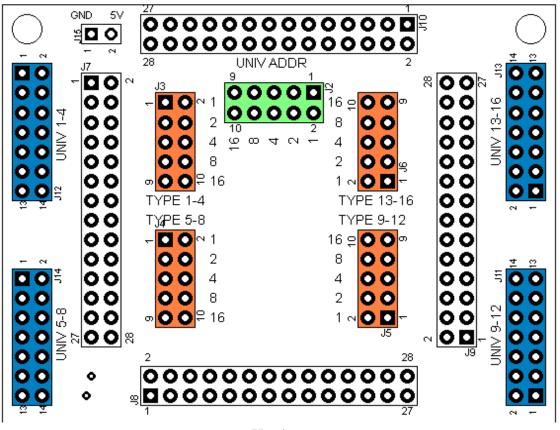

### **OUTPUT TYPE SELECTION:**

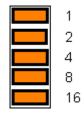

The selection of the output type for each universe is selected with an ten pin header. This provides for 32 types of output pixels. The values are read at power up, so if you change the jumpers, re-apply power. A jumper selects a zero for that particular bit position. If an invalid type is selected the group of universes is set to off. Currently, the jumper on Bit 16 is ignored.

Header types 1-4 sets the output type on header universe 1-4. Header types 5-8 sets the output type on header universes 5-8. Header types 9-12 sets the output type on header universes 9-12. Header types 13-16 sets the output type on header universes 13-16.

| 1<br>2<br>4<br>8<br>0016                                                                                              | 0000 Renard (57.6K): The output header is always 0x7E, 0x80 hex. These values are followed by up to 512 bytes. The special two byte character values for 0x7D, 0x7E, and 0x7F are supported. |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: 0       1         Image: 2       2         Image: 4       8         Image: 0       16                          | <u>0001</u> Renard (115.2K)                                                                                                                                                                  |

| 1<br>002<br>4<br>8<br>0016                                                                                            | <u>0010</u> Renard (230.4K)                                                                                                                                                                  |

| Image: 0       1         Image: 0       2         Image: 0       4         Image: 0       8         Image: 0       16 | <u>0011</u> Renard (460.8K)                                                                                                                                                                  |

| 1<br>2<br>00<br>4<br>8<br>00<br>16                                                                                    | <u>0100</u> DMX: The start byte in the E1.31 is ignored and a 0x00 is always used. The break is 92-96uS, followed by a 12uS NAB. Once the bytes are transmitted, the output remains in idle till the next packet.                                                           |

|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Image: 0       1         Image: 0       2         Image: 0       4         Image: 0       8         Image: 0       16 | 0101 WS2801: The output clock is 781.25KHz, with the data changing on the falling edge. The low data rate is to maintain the data rate simular to other types of output pixels, which are generally around 800KHz. Between each of the bytes there is a half clock delay.   |

| 1<br>002<br>004<br>8<br>0016                                                                                          | Not used - output off                                                                                                                                                                                                                                                       |

| Image: 0       1         Image: 0       2         Image: 0       4         Image: 0       8         Image: 0       16 | Not used 0 output off                                                                                                                                                                                                                                                       |

| 1<br>2<br>4<br>00 8<br>00 16                                                                                          | 1000 WS2811 - The output timing is based on a 12.5MHz clock.<br>The zero output times are<br>0.24/0.96 uS and the one output times are 0.56/0.64 uS. Once the message is sent the<br>output will stay in a low state to load the values.                                    |

| Image: 0       1         Image: 2       2         Image: 4       4         Image: 0       8         Image: 0       16 | <u>1001</u> WS2812B - PREFERRED TIMING FOR WS28XX pixels. The output timing is based on a 12.5MHz clock. The zero output times are 0.40/0.80 uS and the one output times are 0.80/0.48 uS. Once the message is sent the output will stay in a low state to load the values. |

| 1<br>002<br>4<br>008<br>0016                                                                                          | 1010 TM1804 (untested) - The output timing is based on a 12.5MHz clock. The zero output times are 0.48/0.96 uS and the one output times are 0.96/0.48 uS. Once the message is sent the output will stay in a low state to load the values.                                  |

| Image: 0 0 1         Image: 0 0 2         Image: 0 0 4         Image: 0 0 8         Image: 0 0 16                          | 1011 TM1803 & TM1809 (untested) - The output timing is based on a 12.5MHz clock. The zero output times are 0.32/0.64 uS and the one output times are 0.64/0.32 uS. Once the message is sent the output will stay in a low state to load the values.                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>2<br>00<br>4<br>00<br>8<br>00<br>16                                                                                   | 1100 TM1829 (untested) - The output timing is based on a 12.5MHz clock. The zero output times are 0.32/0.88 uS and the one output times are 0.80/0.40 uS. Once the message is sent the output will stay in a high state to load the values.                                                                                                                                      |

| <ul> <li>1</li> <li>2</li> <li>4</li> <li>8</li> <li>1</li> </ul>                                                          | Not used - turns output off                                                                                                                                                                                                                                                                                                                                                      |

| 1<br>002<br>004<br>008<br>0016                                                                                             | Not used - turns output off                                                                                                                                                                                                                                                                                                                                                      |

| I       0       1         I       0       2         I       0       4         I       0       8         I       0       16 | 1111On universes 1-4 this places Renard 56.7K baud outputs 1/2 and DMX on<br>outputs 3/4.<br>On universes 5-8 this places Renard 115.2K baud outputs 5/6 and DMX on<br>outputs 7/8.<br>On universes 9-12 this places Renard 230.4K baud outputs 7/8 and DMX on<br>outputs 11/12.<br>On universes 13-16 this places Renard 460.8K baud outputs 13/14 and DMX<br>on outputs 15/16. |

# OUTPUT TYPE SELECTION:

There is one connector to select the base universe address. The connector has five pins and the jumpers inserted selects a zero for the bit position. The base universe address for board is sixteen. This is shown below:

With all of the jumpers installed this selects a base universe of 16.

| 00000 - 16-31   | 01000 - 128-143  | 10000 - 256-271 | 11000 - 384-399 |

|-----------------|------------------|-----------------|-----------------|

| 00001 - 16-31   | 01001 - 144-1591 | 10001 - 272-287 | 11001 - 400-415 |

| 00010 - 32-47   | 01010 - 160-175  | 10010 - 288-303 | 11010 - 416-431 |

| 00011 - 48-63   | 01011 - 176-191  | 10011 - 304-319 | 11011 - 432-447 |

| 00100 - 64-79   | 01100 - 192-207  | 10100 - 320-335 | 11100 - 448-463 |

| 00101 - 80-95   | 01101 - 208-223  | 10101 - 336-351 | 11101 - 464-479 |

| 00110 - 96-111  | 01110 - 224-239  | 10110 - 352-367 | 11110 - 480-495 |

| 00111 - 112-127 | 01111 - 240-255  | 10111 - 368-383 | 11111 - 496-511 |

|                 |                  |                 |                 |

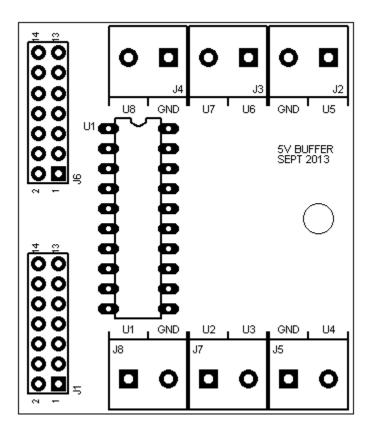

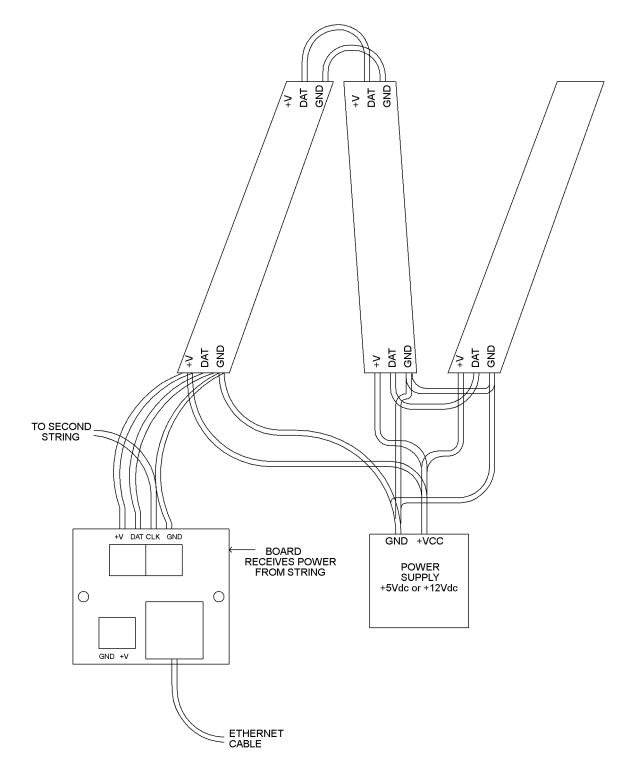

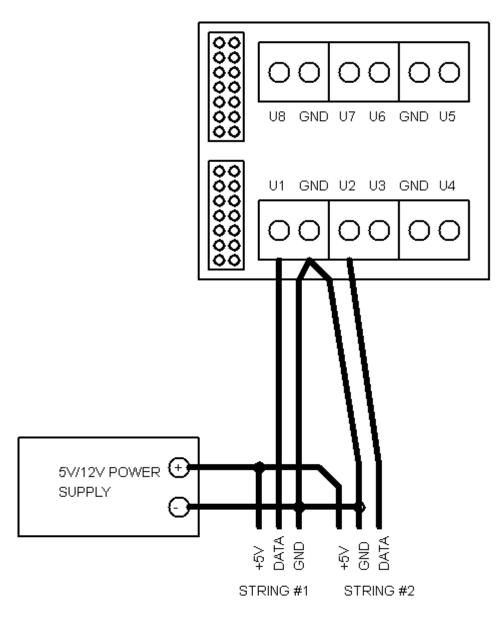

#### 5Vdc Buffer Board

5Vdc Buffer Board

The 5Vdc buffer board is compatible with any two of the universe outputs. The sixteen universe board supports two of these boards. This particular board only supports three channel pixels, so there is no clock output. The driver for the board is a 74ACT541 part, that has higher current than the normal driver to support driving pixels further. The output source termination resistor is 120 ohms, which is chosen to match the impedance of a twisted pair cable (normally 100-120 ohms). Since Ethernet cable is inexpensive, it is recommend to use this for all outputs. The U1-U8 should be on one signal on the pair and the second wire should be connected to ground. Using Ethernet cable, these outputs have driven 50 WS2811 pixels at a 100 feet. Please test your own wiring to ensure that it work for your particular application.

If you are driving 5V pixels, this setup will provide an excellent performance with 33 ohm source termination on the board and 680/170 ohm termination on the receiving end. 170 to +5Vdc and input signal, and 680 to input signal and ground.

All pixels are driven with 5Vdc logic, except for the TLS3XXX series (3.3Vdc inputs). So power the pixels normally from 5V or 12V power. The U1 to U8 outputs correspond to universe outputs 1-8. The ground is shared between the outputs to reduce the connector size.

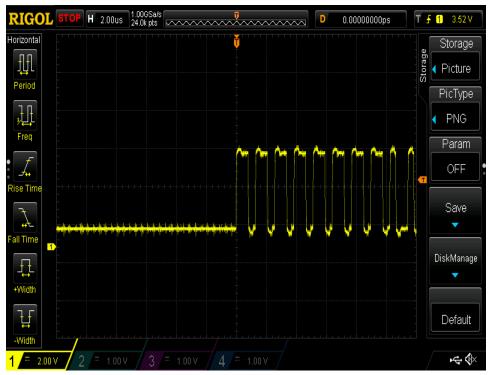

100 Feet With Only Source Termination

100 Feet with 33 Ohm Source Termination and 170/680 Termination

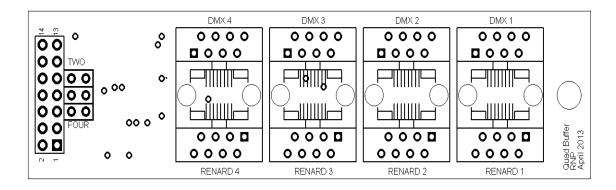

### Quad Output Buffer Board

The quad buffer board is shown below. It supports the output of four universes in either Renard or DMX format. The output buffers are bandwidth limited to 2MHz to limit the noise in your system and to increase maximum cable length. This will help reduce any interference to your FM broadcast. These buffers were tested to cable lengths of 200 feet.

If you are using a three wire pixel format such as serial, DMX, WS2811, the output buffer board can support putting two universes on one cable. When the jumpers on in the four position all connectors are active, if the jumpers are in the two position connectors 1 and 3 are active with two universes each.

The pin out for the Renard on Ethernet cable is shown below:

- 1 Ground

- 2 Ground

- 3 No connect

- 4 Output negative (-)

- 5 Output positive (+)

- 6 No connect

- 7 No connect

- 8 No connect

The pin out for the DMX on Ethernet cable is shown below:

- 1 Data out positive (+) or universe 1

- 2 Data out negative (-) or universe 1

- 3 Clock out positive (+) or universe 2

- 4 No connect

- 5 No connect

- 6 Clock out negative (-) or universe 2

- 7 Ground

- 8 Ground

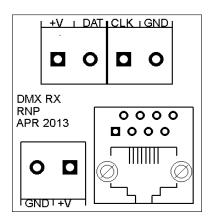

#### DMX Receiver Board

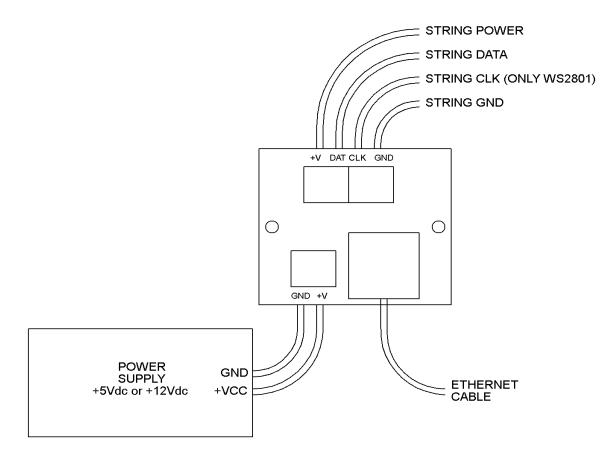

The DMX receiver board can be used with either 5V or 12V pixels. There is an internal regulator that will support either voltage type. The board can either be powered through the power connector or through the power from the pixel string. The receiver supports two channels of RS-485, which can either be a four wire pixel string or two universes of output.

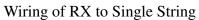

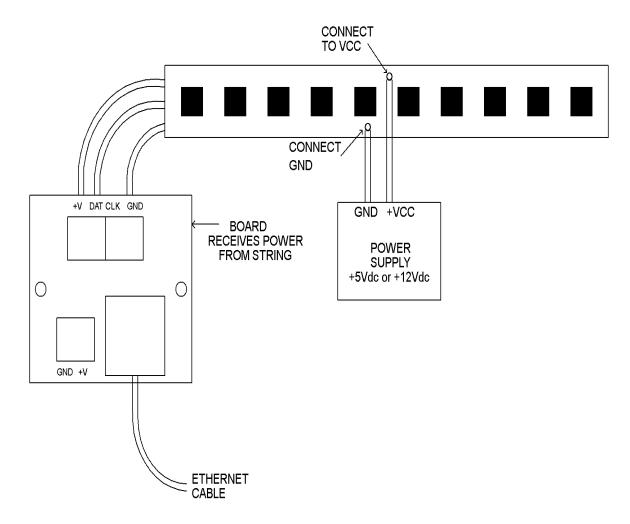

# Example Wiring

RX Receiver, Wiring for Powering From Center of Strip

RX Receiver, Multiple String Wiring and Power

Example Wiring 5V Buffer

#### Revisions

Revision - : Baseline

Revision A : Added gamma correction. Revision B: Added information for revision B board

Revision C: Added information about LED's and to use WS2812 pixel as the standard output.